# DSP-Based Dual Converter – A Few Implementation Related Issues

Atanu Biswas<sup>1</sup>, Snehasish Pal<sup>2</sup> and Suvarun Dalapati<sup>3</sup>

<sup>2</sup>Department of Electrical Engineering, Hooghly Engineering and Technology College, Hooghly,W.B,India.

<sup>1&3</sup>Department of Electrical Engineering,Indian Institute of Engineering Science and Technology, Shibpur, Howrah - 711103, India

Abstract— In UG curriculum of Electrical Engineering, experiments on bi-directional DC drives, employing dual- converter, is often a part of the core UG curriculum. In such cases, custom-made dual converters, controlled by digital controllers and having the desired features and test points may be designed. This paper presents some of the important implementation-based issues, related to the fabrication of a laboratory-based dual- converter, operating in non-circulating-current-mode. The converter is controlled by a two-loop control-strategy, using the Digital Signal Controller dsPIC30F4011. Starting from the basics of dual-converter-operation, the paper gives an overall idea of the scheme and then takes up some of the implementation related issues in details. Exact schematics of actual set-up are presented, along with supporting experimental results, taken from the custom-made laboratory set-up.

Keywords— DC-drive; bi-directional control; dual converter; dsPIC30F4011; interfacing circuits; drivers; filters; SCR; dualloop control

## I. INTRODUCTION

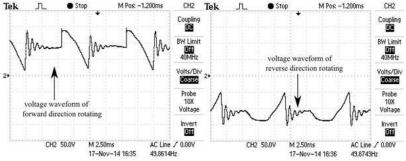

SCR-based dual converters have been one of the classic topics of power-electronics and drives [1-2]. The topic has attracted wide research-interest over the decades [3-13]. While dual-converters have been utilized for different applications such as magnet power supplies [4], DC/DC converters as Inverse Dual Converter [5], cutting applications [6] etc., one of the widest application of this circuit is for achieving four- quadrant control of separately excited DC motors via armature voltage-control [7-12]. Due to the advances in AC drive technology, industrial application of dual-converter-based DC drives has receded over the years. However, academic interest in the subject still exists as it is a part of any UG curriculum on Electrical Engineering in India. Non-circulating current type SCR- based dualconverter (Fig. 1) forms one technique, by which bi-directional speed-control can be demonstrated in a laboratory. Although, such a technique has its own disadvantages like dead-zone and reduction of system gain and non-smooth behaviour during current-transfer [11], the technique also has some advantages like simplicity and low cost due to absence of the inter-phase reactor [11,13]. While a variety of control strategies, involving single [12] or multi-loop structures [9] may be used for such a laboratory set-up, the two-loop based control strategy, using an outer speed-loop and an inner current-loop are most commonly referred to. An outer slower speed loop, with a faster inner current loop, will achieve speed control, while maintaining the armature current within desirable limits [1,2,11]. While such converter-control can be achieved with analogue controllers [9,11], implementation of the lab-set-up using digital controller is advantageous in terms of cost and space-savings. In addition, such a set-up will add flexibility of testing various control strategies by altering the controller-firmware, or optimizing a given control-strategy by changing the parameter-values via firmware. Such implementations, using microprocessors [4,6,11] or digital signal processors [12] have already been attempted. However, keeping all the advantages of such a digital-controller based implementation in mind, it must be admitted that there are issues, which demands careful considerations, while implementing such digital-controller based set-ups in hardware. This paper addresses a few such issues, related to such a fabrication, involving an outer speed-loop and an inner current-loop, based on a single digital signal controller dsPIC30F4011. Some of the hardware issues, such as pulse- timing, feedback signal conditioning and driver-design, are addressed, along with the algorithm for control, in details. This paper is divided into five sections. Section-II presents the theory of a non-circulating current type dual-converter in brief. Section III takes up the implementation issues, such as selection of controller, power-devices and driver-design to make the set-up work successfully. It also addresses related issues, such as feedback signal processing and correct pulse delivery to ensure successful triggering

of SCRs over a wide- range of load and firing angles. Handy design equations are presented along with exact schematics of some of the circuits, related to the above. Section-IV presents some of the experimental results, taken from the fabricated laboratory set- up for dual-converter. Section-V presents the conclusions.

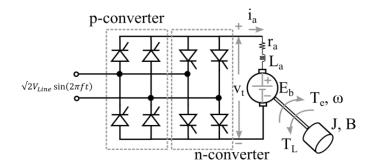

Fig. 1. Basic schematic diagram of a non-circulating-current type dual converter

### I.DSP-BASED DUAL CONVERTER: PRINCIPLES

A dual converter consists of two controlled rectifiers, connected in anti-parallel mode across the armature of a DC motor. Such an arrangement can be used for bi-directional speed control of the connected DC motor, by armature-voltage control principle [1,2,8-11]. A simplified schematic-diagram, showing the non-circulating version of the above scheme is presented in Fig. 1. The basic governing equations, pertaining to the dynamic performance of such a system, in any direction, may be presented as follows:

dt

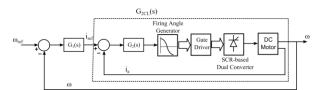

Usually, dual-converter is used for closed-loop speed-control of the connected DC motor. Under such a case, the closed loop feedback scheme may be represented in Fig. 2, and the overall transfer function between the reference-speed-input and the actual output speed may be represented as follows:

$$G_{CL}(s) = \frac{G_1(s)G_{2CL}(s)}{1 + G_1(s)G_{2CL}(s)} \dots (4)$$

The inner-current loop has a faster dynamic response than the outer-speed loop. Care is taken to ensure that the time- constants of the loops are matched, so as to ensure that the reference speed is successfully tracked, while ensuring that the armature-current does not remain above a set limit beyond a particular time-interval. In the following paragraphs, a few implementation-based issues, regarding a dual-converter- driven DC drive, controlled by a DSP-based controller-card using the two-loop control-scheme of Fig. 2, will be addressed.

## **II. IMPLEMENTATION ISSUES**

## A.Selection of Power Devices and Driver Design

The first step in the implementation of the hardware set-up is the selection of power devices for the dual converter,

under consideration. To determine the ratings of the power converter, it is essential to know the armature ratings of the DC motor, to be driven by the dual converter. For the experimental set-up, the motor used had the armature-circuit ratings of 220 V, 6 A.

Assuming that the motor will draw a nearly ripple-free DC current at full-load condition, and taking into account a safety factor of nearly 1.5 for current rating, the minimum average current rating of the SCR required should be around 9 A. Hence, the popularly available SCR model 16TTS12, which is

Fig. 2. A simplified block diagram for closed-loop speed control of a DC motor via dual-converter

having an average current rating of around 10 A and a voltage rating of up to 1600 V, is selected for the dual converter.

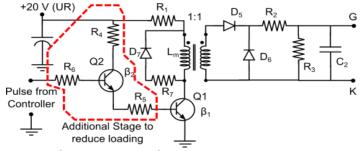

The driver circuit for the SCRs can be designed as per guidelines given in available literature. However, as the drivers will be fed with pulses from a DSP or some CMOS IC (low sourcing capability), a Darlington arrangement at the input-side of the driver may be opted for to reduce the loading effect on the logic ICs. The schematic diagram for such a driver circuit is shown in Fig. 3. The various steps in designing the main and auxiliary transistors for the driver are presented below.

**Step-I:** The main transistor is connected to the primary winding of the pulse-transformer (magnetizing inductance  $L_m$ ). Its voltage and current ratings may be given by (5) and (6).

**Step-II:** In case of the auxiliary transistor, which drives the main transistor, the voltage rating should be at least 24 V (i.e. 20% over the rated value of 20 V), while its current rating is given by:

The value of  $\beta_1$  and  $\beta_2$  may be taken as 10. The values of the resistors may be computed  $R_4$  and  $R_5$  may be computed as follows:

Assuming  $R_5$  to be a small resistance (a few ohms), the value of the base resistance  $R_6$  may now be computed as follows:

$$R_6 = \frac{\beta_1 \beta_2 V_{pulse}}{I_T} - \beta_2 R_5 \dots (9)$$

**Step-III:** A small resistance may be connected in series with the primary of the pulse transformer to protect the transistor and transformer from over-current due to accidental core- saturation. Its value may be computed as follows:

$$R_1 = \frac{24}{I_T} \qquad (10)$$

## B.Selection of Controller

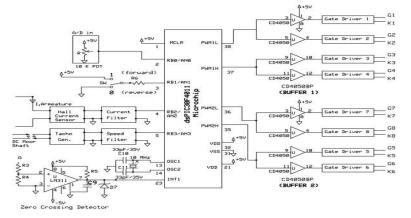

SCR-based dual converter control can be achieved by analogue controllers. However, here the main aim is to implement the control via a digital controller. Many digital controllers, having the minimum required memory, speed and terminal pins can be used for this application. However, to maintain flexibility in programming and also to test the performance of a state-of-the-art digital controller for the above application, a 16-bit microcontroller with an in-built DSP engine, namely dsPIC30F4011 [14], has been used for the above application. It has many powerful peripheral- modules, out of which, two peripherals, namely the PWM port and the ADC port has been used for this application. The ADC module has ten different input pins to scan and digitize ten different input analogue signals. Here, three such pins have been used for feeding in (a) the speed-reference signal, (b) the

Fig. 3. Schematic diagram of the driver circuit for one SCR

speed-feedback signal and (c) the armature current signal. In addition, a direction input (forward or reverse) has also been fed through a separate pin. The PWM port has eight PWM pins, which can be programmed for a variety of power- electronic applications. Four such PWM pins have been used for controlling the eight different SCRs for the dual converter. Fig. 4 presents the schematic of the controller card, based on the above digital controller. Note that to avoid loading on the PWM pins, the output pulses have been transmitted through buffers.

## C.Interfacing for Feedback Control

As shown in Fig. 2, two feedback-signals are required for implementing the dual-loop control-scheme. The outer loop, involving speed-feedback is the slower one, operated by a P-I controller. The inner loop is based on armaturecurrent feedback and is operated by an adaptive hysteresis controller. For a motor, running on no-load or light load, the armature current is far from constant, but has plenty of ripples of twice the supply frequency  $f_s$  Hz over some DC

Fig. 4. The schematic of the controller card used for the dual-converter control application

component. To make the control-scheme work properly, the current must be sensed accurately with linearity and isolation. A suitable Hall-Effect Sensor may be used for this purpose. The Hall-Effect transducer HY-25P has been used for this set-up. Secondly, only the DC component of the current should reach the controller, with the value not

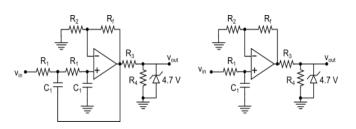

exceeding 5 V (the supply voltage of the DSP). Hence, it is essential to design a low-pass filter to properly filter out the ripples and transmit only the DC component to the controller. A low-pass second order Butterworth-Filter, shown in Fig. 5, is selected for this purpose, since it gives a flat-flat-response. The basic design equations for the low-pass Butterworth filter are presented here, with respect to Fig. 5, for easy reference. These equations can be used directly to design such a filter.

**Step-I:** The cut off frequency of this filter is set at 1/20 of the supply frequency, resulting in the equation:

$$R_1 C_1 = \frac{10}{\pi f_s}$$

-----(11)

Choosing a standard value of C1 (AC capacitor), the value of R1 can be calculated. **Step-II:** The value of Rf and R2 may be calculated by choosing some standard value for R2 and then selecting Rf by using the following equation:

$$\frac{R_f}{R_2} = 0.586$$

-----(12)

**Step-III:**Finally, a potential divider may be placed at the output of the filter so as to make the DC gain of the filter to be unity. The basis of designing this potential-divider network is presented in the following equation:

$$\frac{R_4}{R_3 + R_4} = 0.6305 \tag{13}$$

As the motor-inertia contributes to make the speed signal from the tacho-generator to be "filtered", a second order Butterworth filter may not be needed in this case. However, the designer may re-use (11) - (13) to design a first order Butterworth Filter to suit the application (Fig. 5). Protective Zener diodes (4.7 V, 0.5 W) may be used at the output of each filter to ensure that the voltage remains clamped below 5 V. Suitable scaling by potential-divider circuit may be implemented at critical points to (a) maintain linearity and (b) ensure that eventually the voltage reaching the DSP pin is below 5 V.

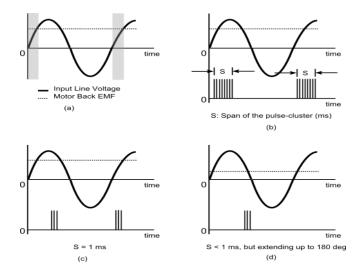

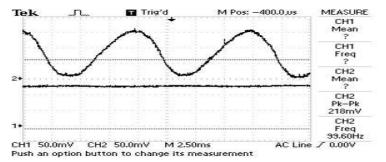

With the properly "conditioned" feedback signals, the controller will work satisfactorily, if correct triggering is achieved at all loads. Usually, at heavy loads (continuous load current with minimal ripple), triggering can be achieved at any firing angle. However, at low and light loads, due to the presence of back-EMF from the motor-armature, a particular triggering angle may not be suitable for turning on the SCR, since it is already reverse-biased due to the back-EMF (Fig. 6). Hence to avoid such issues, the following actions are taken, within the firmware of the controller: • It is ensured that multiple pulses are transmitted for each

# Fig. 5. Second order low pass filter for armature current (left) and 1<sup>st</sup> order low pass filter for speed (right)

Fig. 6. (a) Grey zones showing the regions, where triggering cannot be achieved; (b) firing angle less than  $90^{\circ}$  and pulse-cluster extending up to  $90^{\circ}$ ; (c) firing angle greater than  $90^{\circ}$  and pulse-cluster having a span of 1 ms and (d) pulse cluster extending up to  $180^{\circ}$ , but having a span less than 1 ms

triggering. Such pulse-cluster may span for around 1 ms.

- For all firing angles less than  $90^{\circ}$ , it is ensured that the pulse-cluster is extended till  $90^{\circ}$  or for 1 ms, whichever is more.

- For all firing pulses beyond  $90^{\circ}$ , the pulse-cluster is maintained for 1 ms, or up to  $180^{\circ}$ , whichever is less. The above are illustrated in Fig. 6.

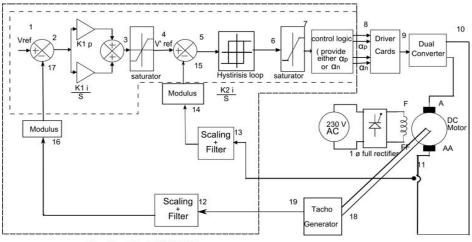

### D.Implementation of the Overall Control Logic via Firmware

The overall control-logic for the dual converter, as per the dual-loop control structure (Fig. 2) has been implemented on the single DSP. The block diagram of the complete system is presented in Fig. 7. The control-algorithm, as implemented via firmware within the DSP may be summarized as below:

- 1. Initialize all necessary modules. Run start-up checks.

- 2. Read the direction command status (forward or reverse); store the same in memory.

- 3. Identify the SCRs to be triggered.

---- Operation within dsPIC 30F4011

Fig. 7. Overall block diagram of the system after implementation of the logic within the DSP via firmware

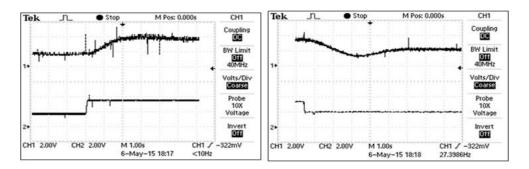

- 4. Read the speed input and speed feedback signals and compute the error and amplify the same through the P-I controller.

- 5. Read the current feedback and compare the same with the P-I controller output (acting as current-reference) to compute the digital hysteresis controller output, which will adjust the firing angle in steps.

- 6. Set the "computation-over flag" and wait till "computation- over flag" is cleared again.

- 7. Once the Zero-Crossing of the line voltage generates the interrupt, go to the interrupt service routine (ISR), generate the appropriate delay (as governed by the computed firing angle) and clear the "computation-over flag".

- 8. Read the status flag (forward or reverse) and compare it with the saved status value. If different from the saved status value, then save this new value in the memory and identify the SCRs to be triggered. Gradually increase the firing angle of the outgoing converter to 180°, stop pulses to all SCRs for around 2 sec, and then trigger the SCRs of the incoming converter at a firing angle of just less than 180° and then gradually reduce the firing angle to reach the original value.

- 9. Go to step no. 4.

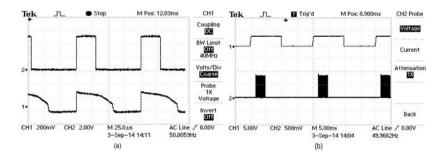

#### IV.RESULTS FROM THE EXPERIMENTAL SET-UP

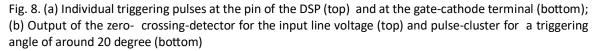

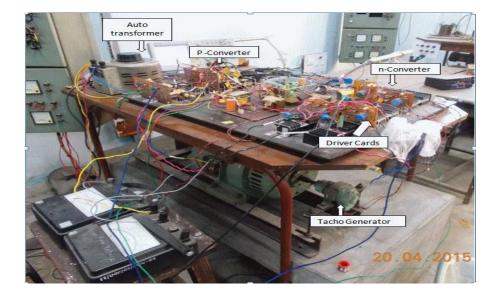

The above logic was implemented via a C30 program, written in the MPLAB environment and loaded on to the controller via the ICSP programmer. Upon successful implementation of the hardware circuit and the allied firmware, the set up gave acceptable results, some of which are presented in this section in Figs. 8 - 12. A photograph of the fabricated laboratory set-up is shown in Fig. 13.

## V.CONCLUSION

Some implementation based issues, related to the fabrication of a laboratory set-up for a DSP-controlled dualconverter fed DC motor drive is discussed in this paper. Issues such as the use of Darlington-pair transistors for the drivers, correct pulse-cluster-span for various firing angles to ensure successful triggering under various loading conditions, use of correctly designed filters for current and speed feedback signals and scaling and amplification thereof have been presented. Some of the experimental results from the fabricated laboratory set-up have also been added to show that the implemented hardware and firmware are working correctly.

Fig. 9. Actual armature current (top) and filtered and amplified version after passing through the low pass Butterworth Filter (bottom); Scale: Y-axis: 2 A/div (both channels), X-axis: 2.5 ms/div.

Fig. 10. Output voltage waveform of the dual converter on light load in forward direction (left) and reverse direction (right), illustrating successful SCR triggering

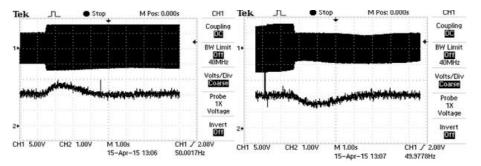

Fig. 11. Actual speed (top) following reference speed (bottom) for a step-increase (left) and for a step-decrease (right) in the reference signal

Fig. 12. Input voltage envelope experiencing a sudden rise (left) and fall (right) (Y-axis: 200 V / div); Bottom: Speed of the motor first experiences a transient disturbance then comes back to the set value in both the cases (Y-axis: 500 rpm/div); X-axis: 1 sec / div (for both channels)

Fig. 13. A picture showing the various components of the experimental set-up

## References

- N. Mohan, T. Undeland, and W. P. Robbins, Power Electronics: Converters, Applications, and Design, 2<sup>nd</sup> ed., John Wiley & Sons, New York, 2001, pp. 383-396.

- [2] G. K. Dubey, Fundamentals of Electrical Drives, Narosa Publishing House, New Delhi, 1995.

- [3] T. Sebastian and S. B. Dewan, "Comparison of dual-converter-based power supply systems," IEEE Trans. Ind. Applicat., vol. 25, pp. 339-347, March/April 1989.

- [4] J. M. S. Kim and S. B. Dewan, "Closed-loop voltage regulation of dual converters with circulating-current mode, used in four-quadrant dc magnet power supplies," IEEE Trans. Ind. Applicat., vol. 27, pp. 1026- 1033, November/December 1991.

- [5] M. Ehsani, I. Hussain, and M. Oruc Bilgic, "Inverse dual converter (IDC) for high-power dc-dc applications," IEEE Trans. Power Electron., vol. 8, pp. 216-223, April 1993.

- [6] M. K. Shrivastava, C. V. Abroal, M. K. H. Kalla, and B. Sarkar, "Microprocessor based dual converter control of on line tube cutting machine," in Proc. Power Electronics, Drives and Energy Systems for Industrial Growth (PEDES), 1996, vol. 2, pp. 845-849.

- [7] D. L. Duff and A. Ludbrook, "Reversing thyristor armature dual converter with logic crossover conrol," IEEE Trans. Industry and General Applications, pp. 216-222, May/June 1965.

- [8] G. Revankar and D. S. Sabnis, "Analysis of dual converter system," IEEE Trans. Ind. Electron. & Control Instrumentation, vol. IECI-22, pp. 55-61, February 1975.

- [9] T. Krishnan and B. Ramaswamy, "Speed control of dc motor using thyristor dual converter," IEEE Trans. Ind. Electron. & Control Instrumentation, vol. IECI-23, pp. 391-399, November 1976.

- [10] M. J. Er, "A smart gain digital controller for a dual converter fed dc drive," in Conf. Rec. IEEE Ind. Electron. Society Annu. Conf. (IECON), 1988, pp. 853-858.

- [11] B. H. Khan, S. R. Doradla and G. K. Dubey, "A new simultaneous gating GTO dual converter-fed dc motor drive without circulating current," IEEE Trans. Ind. Applicat., vol. 27, pp. 560-566, May/June 1991.

- [12] S. Kumar and A. Deshpande, "DSP based close-loop speed control system for dc motor using dual converter," in Conf. Rec. IEEE Annual India Conference (INDICON) 2014.

- [13] J. K. Ji and S. K. Sul, "Operation analysis and new current control of parallel connected dual converter system without interphase reactors," in Proc. IEEE Industrial Electronics Society Annual Conference (IECON), 1999, vol. 1, pp. 235-240.

- [14] "dsPIC30F4011/12 datasheet: high performance 16-bit digital signal controllers," Microchip Technology, 2010.