# Level Inverter

Jahnvi Srivastava

Department of Electrical

Engineering

Power System & Control

Vishwavidyalaya Engineering

College Ambikapur

Maheedhar Dubey

Assistant professor

Department of Electrical Engineering

Power System & Control

Vishwavidyalaya Engineering

College Ambikapur

Manoj Kumar Dewangan

Assistant professor

Department of Electrical Engineering

Power System & Control

Vishwavidyalaya Engineering

College Ambikapur

ISSN NO: 1844-8135

Abstract - The rapid adoption of multi-level inverters in electric drives and renewable energy systems highlights their crucial role in modern power electronics. These inverters provide significant advantages over traditional two-level inverters, such as reduced dv/dt stress, lower total harmonic distortion (THD), and decreased common mode current. However, common multilevel inverter topologies, like neutral point clamped, cascaded H-bridge, and flying capacitor inverters, encounter challenges that hinder optimal performance. This paper introduces an innovative three-phase two-level inverter topology designed to address common mode voltage and current issues found in existing designs. The proposed topology combines two cascaded converters and uses device junction capacitance (DJC) to implement a neutral point clamping methodology, enhancing the inverter's stability and efficiency. A detailed analysis using the switching function concept demonstrates the impact of DJC on inverter performance. The study also presents an advanced PWM control scheme to optimize the modulation process and minimize common mode voltage variations. MATLAB simulation results show the proposed topology's superiority over conventional and H7 two-level inverters, with significant improvements in key performance metrics such as pole voltage, phase voltage, common mode voltage, and THD. The proposed inverter reduces THD to 61.41%, compared to 91.81% and 88.01% for conventional and H7 inverters, respectively.

This research not only advances the field of power electronics but also provides practical insights for engineers and researchers. By addressing critical issues in multi-level inverter design, the proposed topology paves the way for more efficient and reliable power conversion systems, contributing to enhanced energy efficiency and sustainability in contemporary applications.

Keywords— Multi-level inverters, three-phase inverters, common mode voltage, device junction capacitance (DJC), pulse width modulation (PWM), total harmonic distortion (THD), neutral point clamping.

### Introduction

In contemporary applications, the importance of multi-level inverters is paramount, especially in electric drives and renewable energy systems. Their adoption is driven by advantages over traditional two-level inverters, including reduced dv/dt stress, lower total harmonic distortion (THD), and decreased common mode current. Despite their appeal, existing multi-level inverter topologies, such as neutral point clamped, cascaded H-bridge, and flying capacitor inverters, have their limitations.

The neutral point clamped multi-level inverter, though widely used, faces issues like neutral point fluctuations, compromising system stability and performance. The cascaded H-bridge multi-level inverter requires independent DC sources, adding complexity and cost. The flying capacitor multi-level inverter, while promising, struggles with charging flying capacitors, introducing operational and control complexities.

Given these limitations, there is a need for novel solutions that can overcome these challenges while leveraging the advantages of multi-level inverters. This paper proposes a new three-phase two-level inverter topology designed to address common mode voltage and current issues. Building on prior research and insights from existing topologies, our novel approach aims to balance performance, efficiency, and complexity.

The primary goal of this study is to explore the proposed topology comprehensively, elucidating its performance characteristics and potential applications across various scenarios. Through rigorous analysis and simulation, we aim to demonstrate the efficacy of our design in mitigating common mode voltage and current while maintaining system efficiency and reliability.

Furthermore, our investigation extends to examining the impact of the proposed topology on electromagnetic compatibility, a crucial aspect in modern power electronics systems. Addressing these aspects is vital for ensuring seamless integration and operation of multi-level inverters in real-world applications.

In conclusion, this research not only advances power electronics but also serves as a practical guide for engineers and researchers in the field of multi-level inverter design. As the demand for efficient and reliable power conversion systems increases, innovative solutions like the one proposed here are key to enhancing energy efficiency and sustainability.

I. PROPOSED TOPOLOGY OF THE THREE-PHASE TWO-LEVEL CMLI

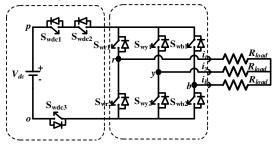

The circuit of the proposed three phase two level CMLI is shown in Fig.1

Fig.1 Circuit diagram of the proposed three-phase two-level CMLI

The circuit schematic of the proposed three-phase three-level inverter connected to a resistive load is shown in Fig. 1. The DC voltage source having a magnitude of ' $V_{dc}$ ' is connected to Converter '1' between the input terminals 'p' and 'o' of the three-phase three-level inverter. The proposed three-level inverter consists of a two-level inverter and three freewheeling switches  $S_{wdc1}$ ,  $S_{wdc2}$ , and  $S_{wdc3}$ . The three-phase output terminals 'r', 'y' and 'b' of the three-phase three-level inverter are connected to the resistive load ' $R_{load}$ '.

The topology consists of two cascaded converters, viz. Converter 1 and Converter 2. Converter 1 consists of 3 switches –  $S_{wdc1}$ ,  $S_{wdc2}$  and  $S_{wdc1}$ . This converter aids in neutral point clamping during the common zero states. Converter 2 is a regular three phase bridge inverter circuit, composed by the six switches,  $S_{wr1}$ ,  $S_{wr2}$ ,  $S_{wy1}$ ,  $S_{wy2}$ ,  $S_{wb1}$  and  $S_{wb2}$ . A dc voltage  $V_{dc}$  is connected to the input side of Converter 1. The output terminals r, y and b of the inverter are connected to resistive load. The currents flowing through phases r, y and b have been represented as ir, iv and ib, respectively.

The most notable feature of this inverter circuit is the usage of device junction capacitance in converter 1 and converter 2 to implement neutral point clamping methodology for the reduction of common mode voltage. Freewheeling in converter 2 is taken care. During normal operation of inverter converter '1' is freewheeling i.e., when switch  $S_{WX12}$ , where x = 'r', 'y', 'b' are under operation. Converter '2' is in freewheeling i.e., when switch  $S_{WX12}$ , where x = 'r', 'y', 'b' are in on state, when converter '1' is under operation.

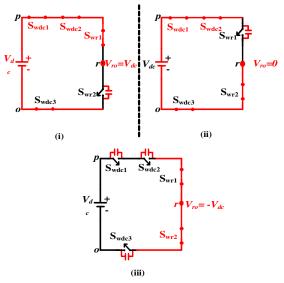

The three-phase two-level inverter normally generates two levels 'Vdc' and '0' in the pole voltage. Whenever any of the upper switch 'Swx1' where 'x' = 'r', 'y' and 'b' in the three-phase two-level inverter are turned ON, then a pole voltage 'Vdc' will be generated in the corresponding pole voltage as shown in Fig. 2(i). Similarly, whenever any of the lower switch 'Swx2' in the three-phase two-level inverter is turned ON, then a pole voltage '0' will be generated in the corresponding pole voltage as shown in Fig. 2. (ii) The DJC [9] is the capacitance across the power semiconductor switch. In the case of MOSFET, the DJC will be across the drain and source whereas for the IGBT the DJC will be across the emitter and collector. The

circuit schematic of three-phase two-level inverter by incorporating the DJC is shown in Fig. 3(a).

ISSN NO: 1844-8135

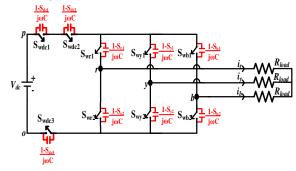

# III. Analysis of two-level inverter using switching function concept including the effect of DJC

For analyzing the effect of DJC on the two-level inverter, the switching function concept is used. Fig. 3 shows the circuit of a two-level inverter with the switching function incorporated DJC. Whenever, the switch ' $S_{wxk}$ ' where 'x'='r', 'y' and 'b' and 'k'='1' and '2' is turned ON, then the switching function ' $S_{xk}$ ' for the corresponding switch will be equal to '1'. As a result, the magnitude of the impedance across the switch will be equal to zero and the effect of DJC across the switch will be neglected. Whenever, the switch ' $S_{xk}$ ' is turned OFF, then the switching function ' $S_{xk}$ ' for the corresponding switch will be equal to '0'. As a result, the magnitude of the impedance across the switch will be equal to ' $1/j_{D}$ C' due to the effect of DJC across the switch. In order to study the effect of DJC on the two-level inverter, the expressions for the pole voltages and phase voltage of the two-level inverter need to obtained.

Fig.2 Circuit schematic of three-phase two-level inverter considering DJC.

Fig. 3 Circuit schematic of three-phase two-level inverter by incorporating the DJC.

From Fig. 3, the expression for the pole voltages ' $v_{ro}$ ', ' $v_{yo}$ ' and ' $v_{bo}$ ' are given by

$$\begin{split} V_{ro} &= \frac{\frac{V_{dc}}{j\omega_c} \times \left( \left( 1 - S_{r2} \right) + \left( 1 - S_3 \right) \right)}{\frac{1}{j\omega_c} \left( \left( 1 - S_{r2} \right) + \left( 1 - S_{r1} \right) + \left( 1 - S_1 \right) + \left( 1 - S_2 \right) + \left( 1 - S_3 \right) \right)} \\ V_{ro} &= \frac{V_{dc} \times \left( \left( 1 - S_{r2} \right) + \left( 1 - S_3 \right) \right)}{\left( \left( 1 - S_{r2} \right) + \left( 1 - S_{r1} \right) + \left( 1 - S_1 \right) + \left( 1 - S_2 \right) + \left( 1 - S_3 \right) \right)} \end{split}$$

Similarly for phase 'y' is given as:

$$\begin{split} V_{yo} &= \frac{\frac{V_{dc}}{j\omega_{c}} \times \left( \left( 1 - S_{y2} \right) + \left( 1 - S_{3} \right) \right)}{\frac{1}{j\omega_{c}} \left( \left( 1 - S_{y2} \right) + \left( 1 - S_{y1} \right) + \left( 1 - S_{1} \right) + \left( 1 - S_{2} \right) + \left( 1 - S_{3} \right) \right)} \\ V_{ro} &= \frac{V_{dc} \times \left( \left( 1 - S_{y2} \right) + \left( 1 - S_{3} \right) \right)}{\left( \left( 1 - S_{y2} \right) + \left( 1 - S_{1} \right) + \left( 1 - S_{3} \right) + \left( 1 - S_{3} \right) \right)} \end{split}$$

Similarly for phase 'b' is given as:

$$V_{bo} = \frac{\frac{V_{dc}}{j\omega_{c}} \times ((1 - S_{b2}) + (1 - S_{3}))}{\frac{1}{j\omega_{c}} ((1 - S_{b2}) + (1 - S_{b1}) + (1 - S_{1}) + (1 - S_{2}) + (1 - S_{3}))} \qquad \frac{V_{r}}{V_{y}}$$

$$V_{bo} = \frac{V_{dc} \times ((1 - S_{b2}) + (1 - S_{3}))}{((1 - S_{b2}) + (1 - S_{b1}) + (1 - S_{1}) + (1 - S_{2}) + (1 - S_{3}))} \qquad \frac{V_{b}}{V_{b}}$$

For the ease of calculation let us consider  $S_{r1}$ '=  $(1-S_{r1})$ ,  $S_{r2}$ '=  $(1-S_{r2})$ ,  $S_{y1}$ '=  $(1-S_{y1})$ ,  $S_{y2}$ '=  $(1-S_{y2})$ ,  $S_{b1}$ '=  $(1-S_{b1})$ ,  $S_{b2}$ '=  $(1-S_{b2})$  and  $S_{123}$ '= $(1-S_1)$  +  $(1-S_2)$ +  $(1-S_3)$

Common mode voltage is given as:

$$\begin{split} V_{cm} = & \frac{V_{ro} + V_{bo} + V_{yo}}{3} \\ V_{dc} \times & \left( S_{r2} + (1 - S_3) \right) \\ & \left( S_{r1} + S_{r2} + (1 - S_1) + (1 - S_2) + (1 - S_3) \right) + \\ V_{cm} = & \frac{1}{3} \begin{pmatrix} V_{dc} \times \left( S_{y2} + (1 - S_3) \right) \\ & \left( S_{y1} + S_{y2} + (1 - S_1) + (1 - S_2) + (1 - S_3) \right) \\ & \left( S_{b1} + S_{b2} + (1 - S_1) + (1 - S_2) + (1 - S_3) \right) \end{pmatrix} + \\ & \frac{V_{dc} \times \left( S_{b2} + (1 - S_3) \right)}{\left( S_{b1} + S_{b2} + (1 - S_1) + (1 - S_2) + (1 - S_3) \right)} \end{split}$$

The phase voltages ' $v_{xn}$ ' can be obtained by subtracting the pole voltages ' $v_{xo}$ ' and common mode voltage ' $v_{cm}$ '

$$\begin{split} V_{ry} &= \frac{nm1}{\left(S_{r1}^{'} + S_{r2}^{'} + S_{wdc\_123}^{'}\right) \times \left(S_{y1}^{'} + S_{y2}^{'} + S_{wdc\_123}^{'}\right) \times \left(S_{b1}^{'} + S_{b2}^{'} + S_{wdc\_123}^{'}\right)} \\ V_{yb} &= \frac{num2}{\left(S_{y2}^{'} + S_{y1}^{'} + S_{123}^{'}\right) * \left(S_{b2}^{'} + S_{b1}^{'} + S_{123}^{'}\right)} \end{split}$$

$$\begin{split} &V_{rb} = \frac{num3}{\left(S_{r2}^{'} + S_{r1}^{'} + S_{123}^{'}\right) * \left(S_{b2}^{'} + S_{b1}^{'} + S_{123}^{'}\right)} \\ &num1 = V_{dc} \times \begin{pmatrix} \left(S_{r2}^{'} + S_{3}^{'}\right) \times \left(S_{y2}^{'} + S_{y1}^{'} + S_{123}^{'}\right) \\ - \left(S_{y2}^{'} + S_{3}^{'}\right) \times \left(S_{r2}^{'} + S_{r1}^{'} + S_{123}^{'}\right) \end{pmatrix} \\ &num2 = V_{dc} \times \begin{pmatrix} \left(S_{y2}^{'} + S_{3}^{'}\right) * \left(S_{b2}^{'} + S_{b1}^{'} + S_{123}^{'}\right) \\ - \left(S_{b2}^{'} + S_{3}^{'}\right) * \left(S_{y2}^{'} + S_{y1}^{'} + S_{123}^{'}\right) \end{pmatrix} \\ &num3 = V_{dc} \times \begin{pmatrix} \left(S_{r2}^{'} + S_{3}^{'}\right) * \left(S_{b2}^{'} + S_{b1}^{'} + S_{123}^{'}\right) \\ - \left(S_{b2}^{'} + S_{3}^{'}\right) * \left(S_{r2}^{'} + S_{r1}^{'} + S_{123}^{'}\right) \end{pmatrix} \end{split}$$

ISSN NO: 1844-8135

Using the expression (1)-(7), the analytical waveform of pole voltages, phase voltages and common mode voltage can be obtained.

### III. CONTROL SCHEME

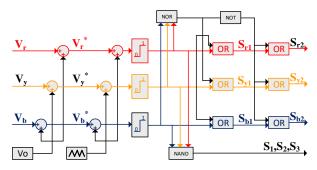

Fig.4 Proposed PWM modulator.

**Table.1 Switching Sequence**

| $S_{r1}$ | $S_{r2}$ | $S_{y1}$ | S <sub>y2</sub> | $S_{b1}$ | $S_{b2}$ | $S_1$ | $S_2$ | $S_3$ | $V_{cm}$            |

|----------|----------|----------|-----------------|----------|----------|-------|-------|-------|---------------------|

| 1        | 0        | 0        | 1               | 0        | 1        | 1     | 1     | 1     | V <sub>dc</sub> /3  |

| 1        | 0        | 1        | 0               | 0        | 1        | 1     | 1     | 1     | 2/3*V <sub>dc</sub> |

| 1        | 0        | 0        | 1               | 1        | 0        | 1     | 1     | 1     | 2/3*V <sub>dc</sub> |

| 0        | 1        | 0        | 1               | 1        | 0        | 1     | 1     | 1     | $V_{dc}/3$          |

| 0        | 1        | 1        | 0               | 1        | 0        | 1     | 1     | 1     | $2/3*V_{dc}$        |

| 0        | 1        | 1        | 0               | 0        | 1        | 1     | 1     | 1     | V <sub>dc</sub> /3  |

| 1        | 1        | 1        | 1               | 1        | 1        | 0     | 0     | 0     | V <sub>dc</sub> /3  |

The implementation of the proposed MDPWM is discussed. The overall block diagram for the proposed PWM is shown in Fig.4. where  $V_r$ ,  $V_y$ , and  $V_b$  are the original sinusoidal reference signals,  $V_0$  is the zero-sequence signal,  $V_0$  is calculated via the magnitude test as follows

$$V_0 = \left[ sign(V_{\min}) \right] \left( \frac{V_{dc}}{2} \right) - V_{\min}$$

where  $V_{\text{min}}$  is the original sinusoidal reference  $(V_r,\,V_y,\,\text{or}\,\,V_b)$  with the minimum magnitude.

After the injection of  $V_0$ , the resultant modulation signals  $(V_r^*, V_y^* \text{ and } V_b^*)$  are then compared with a triangular carrier wave to generate the logic signals.

From the intermediate pulses, the final pulses ' $S_{wr1}$ ', ' $S_{wy1}$ ' and ' $S_{wb1}$ ' are obtained by using OR logic gate as shown in Fig.4. The pulses ' $S_{wr2}$ ', ' $S_{wy2}$ ' and ' $S_{wy2}$ ' are obtained from the pulses ' $S_{wr1}$ ', ' $S_{wy1}$ ' and ' $S_{wy1}$ ' using OR logic and NOT logic gates as shown in Fig.5. In order to generate PWM with one zero vector ( $S_1,S_2,S_3$ ), simple logic operations where  $S_r$ ,  $S_y$  and  $S_b$  are applied NAND logic to generate the desired gating signals. The switching sequence obtained using above control scheme is shown in Table.1

#### II. SIMULATION RESULT

In order to verify the operation of three-phase two-level inverter which generates two levels in the pole voltage and reduced levels in common mode voltage by incorporating the device junction capacitance (DJC), a simulation is done using MATLAB software. The parameters used for the simulation are  $V_{\rm dc}\!\!=\!\!400$  V and  $R_{\rm load}\!=\!\!100$  ohm. To analyze the performance improvement of three-phase inverter a comparative analysis of conventional inverter, H7 inverter and proposed inverter is shown in Fig 4.

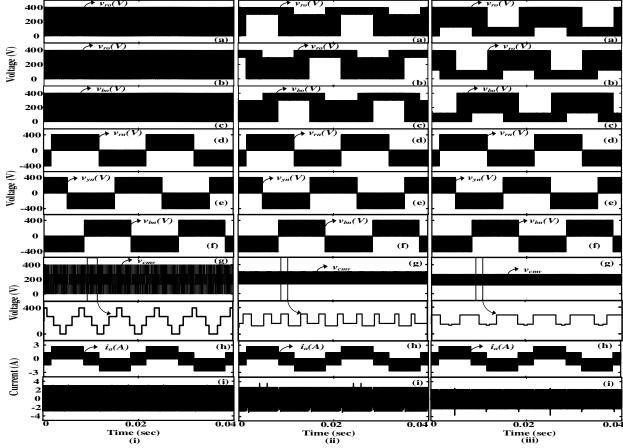

The subplots (a)-(c) of Fig.5(i), Fig.5(ii) and Fig.5(iii) shows the waveforms of the pole voltages 'vro', 'vyo' and 'vbo' for the conventional two-level inverter, H7 two-level inverter and the proposed two-level inverter (considering DJC). The subplots (d)-(f) of Fig.5(i) and Fig.5(ii) shows the waveform of the phase voltages 'vrn', 'vyn' and 'vbn'. The maximum value of the output voltage in all the switching combinations is 400V. The subplot (g) of Fig.5(i), Fig.5(ii) and Fig.5(iii) shows the waveform of the common mode voltage 'vcm'. And subplot (h) shows the zoomed version of common mode voltage. The magnitude of 'vcm' in a conventional two-level inverter is 0 to V<sub>dc</sub>, in H7 two-level inverter magnitude of ' $v_{cm}$ ' is  $V_{dc}/3$  to  $2V_{dc}/3$  whereas in proposed the two-level H9 inverter (considering DJC) magnitude of 'v<sub>cm</sub>' is V<sub>dc</sub>/3 to 2V<sub>dc</sub>/3, but in this method change in common mode voltage with respect to time is less as compared with H7 two level inverter It is verified the simulation that an additional level is absent in proposed model. The subplots (i) shows the current waveform of two-level inverter and subplots (j) shows the common mode current icmc of the three different topologies as discussed.

ISSN NO: 1844-8135

Fig.5 Simulation waveforms of the (i) conventional inverter (ii) two-level inverter H-7, and (iii) proposed two-level inverter H9. (a)-(c) pole voltages  $v_{ro}$ ',  $v_{yo}$ ' and  $v_{bo}$ ', (d)-(f) phase voltages  $v_{rn}$ ',  $v_{yn}$ ' and  $v_{bn}$ ', (g) common mode voltage (h) zoomed version of common mode voltage, (i) current waveform and (j) common mode current  $i_{cmc}$

**Fig.6** FFT spectrum of the (i) conventional inverter (ii) H7 inverter, and (iii) proposed two-level inverter, (a) phase voltage (b) output current

Fig.6 (a) shows the waveforms of the FFT spectrum in the phase voltage of the (i) conventional inverter (ii) two-level inverter H-7, and (iii) proposed two-level inverter. The THD of the phase voltage of a conventional two-level inverter is around 91.81% whereas for the H7 two-level inverter, the THD is around 88.01% and for the proposed two-level inverter THD is 61.41%. Fig.6 (b) shows the waveforms of the FFT spectrum of the current of (i) conventional inverter (ii) two-level inverter H-7, and (iii) proposed two-level inverter. The THD of the phase voltage of a conventional two-level inverter is around 91.78% whereas for the H7 two-level inverter, the THD is around 88.00% and for the proposed two-level inverter THD is 61.42%.

#### Conclusion

In conclusion, our research presents a pioneering solution to common mode voltage and current issues in multi-level inverters, offering a promising avenue for advancing power electronics systems' efficiency and reliability. As the demand for high-performance power conversion systems continues to rise, innovative solutions like ours hold the potential to drive substantial progress in energy efficiency and sustainability.

#### REFERENCES

- P. R. Kumar, P. P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon and L. G. Franquelo, "A Three-Level Common-Mode Voltage Eliminated Inverter With Single DC Supply Using Flying Capacitor Inverter and Cascaded H-Bridge," in IEEE Transactions on Power Electronics, vol. 29, no. 3, pp. 1402-1409, March 2014, doi: 10.1109/TPEL.2013.2262808.

- [2] J. Huang and H. Shi, "Reducing the Common-Mode Voltage through Carrier Peak Position Modulation in an SPWM Three-Phase Inverter," in IEEE Transactions on Power Electronics, vol. 29, no. 9, pp. 4490-4495, Sept. 2014, doi: 10.1109/TPEL.2014.2303897.

[3] C. T. Morris, D. Han and B. Sarlioglu, "Reduction of Common Mode Voltage and Conducted EMI Through Three-Phase Inverter Topology," in IEEE Transactions on Power Electronics, vol. 32, no. 3, pp. 1720-1724, March 2017, doi: 10.1109/TPEL.2016.2608388.

ISSN NO: 1844-8135

- [4] Hota and V. Agarwal, "Novel Three-Phase H10 Inverter Topology With Zero or Constant Common-Mode Voltage for Three-Phase Induction Motor Drive Applications," in IEEE Transactions on Industrial Electronics, vol. 69, no. 7, pp. 7522-7525, July 2022, doi: 10.1109/TIE.2021.3097656.

- [5] A. Hota and V. Agarwal, "A New Three-Phase Inverter Topology for Reducing the dv/dt and Peak-to-Peak Value of Common Mode Voltage," in IEEE Transactions on Industrial Electronics, vol. 69, no. 12, pp. 11979-11986, Dec. 2022, doi: 10.1109/TIE.2022.3140517.

- [6] S. Takahashi, S. Ogasawara, M. Takemoto, K. Orikawa and M. Tamate, "Common-Mode Voltage Attenuation of an Active Common-Mode Filter in a Motor Drive System Fed by a PWM Inverter," in IEEE Transactions on Industry Applications, vol. 55, no. 3, pp. 2721-2730, May-June 2019, doi: 10.1109/TIA.2019.2892364.

- [7] T. -D. Duong, M. -K. Nguyen, T. -T. Tran, D. -V. Vo, Y. -C. Lim and J. -H. Choi, "Three-Phase Impedance-Source Inverter With Common-Mode Voltage Reduction," in IEEE Access, vol. 9, pp. 164510-164519, 2021, doi: 10.1109/ACCESS.2021.3134996.

- [8] X. Deng, H. Wang, X. Zhu, H. Wang, W. Zhang and X. Yue, "Common-Mode Voltage Reduction and Neutral-Point Voltage Control Using Space Vector Modulation for Coupled Ten-Switch Three-Phase Three-Level Inverter," in IEEE Transactions on Power Electronics, vol. 37, no. 6, pp. 6397-6411, June 2022, doi: 10.1109/TPEL.2021.3133714.

- [9] T. K. S. Freddy, N. A. Rahim, W. -P. Hew and H. S. Che, "Modulation Techniques to Reduce Leakage Current in Three-Phase Transformerless H7 Photovoltaic Inverter," in IEEE Transactions on Industrial Electronics, vol. 62, no. 1, pp. 322-331, Jan. 2015, doi: 10.1109/TIE.2014.2327585.

- [10] L. Concari, D. Barater, G. Buticchi, C. Concari and M. Liserre, "H8 Inverter for Common-Mode Voltage Reduction in Electric Drives," in IEEE Transactions on Industry Applications, vol. 52, no. 5, pp. 4010-4019, Sept.-Oct. 2016, doi: 10.1109/TIA.2016.2581763.