### LITERATURE REVIEW ON DATA COMPRESSION TECHNIQUES USING LOSSLESS ALGORITHM

Thanam Pullaiah1Dr.K.Manjunathachari2Dr.B.L.Malleswari3Research Scholar, JNTU-H,Prof. & Head, Dept. of ECE,Professor& PrincipalAsst.Prof.,ECE,VMTW-Hyderabad, GITAM University, Hyderabad.SriDevi Women's Engineering CollegeTelangana, IndiaTelangana, IndiaTelangana, India.

# ABSTRACT

With the contemporary design regard to shift in a chip enlargement the amount of processing elements, high-bandwidth [1] hold-up in on-chip linkage is indispensable for low-speed communication. Utmost of the preceding work hived on architectures of router and webbing topography using broad buses. Although such results may proceed in a complex router planning and cost. In this report, we utilize a table-based information technique of compression, depending on a design value in traffic hoard. Compressing huge packet into a little one can enlarge the effectual of routers bandwidth and connection, while preserving power due to decrease in performance. The foremost challenges are furnish a scalable execution of tables and reducing high up of the compression speed .Initial, we present a split table scheme that requires one encrypting and one decrypting tables for every transforming element, a regulation protocol that does not need orderly delivery. Then, we present smooth encrypt that merge flit inoculation and encrypting in a conduit. Moreover, compression of data can be particular applied to transmission on overfull paths only if compression enhances performance. Simulation outcome in a CMP 16-core exhibit that our consolidation technique increases packet speed to 44% with the mean of 32% and turn down the webbing consumption of power by 44% medial.

**KEYWORDS**: on-chip, communications, data compression, lossy, lossless data

communication

# I. INTRODUCTION

Data compression method is a low cost method, for enhancing speed [2] and bandwidth [3] with in specified architecture. Reducing redundancy information permits to be saved in less physical bits and to be sent in less cycles across a fixed number of busses. To reduce the bandwidth and storage capability of digital modules data compressions algorithms play a important role. Lossless compression algorithms are essential in communications systems. Lossy compression is a approximation technique well suited for audio and video applications. Basically lossy compression system will produce higher compression rate compare with the loss less data compression but it nowhere related to source data. lossy compression [5-8] method advised globally for H.264 [4] and JPEG etc applications. Conventionally loss less data compression technique is applied where data content does not change in information across any stage like compression and decompression. Loss less data compression method play a critical role in research to manage the data base information, binary data, text, html data where compression and decompression required at source, destination end. Loss less data compression

methods mainly used in medical, video applications because every bit will contains critical information.

### **II.METHODOLOGY**

In communication system data compression plays an important role. This leads to increase the speed and decrease the delay in transferring the data like images, videos. the following are the methodology had been used they are

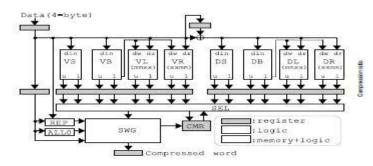

A. In X-hash encoder algorithm is used to calculate a partial-matching word from dictionaries based up on the hash value, has value calculated based on word length with mean value. Problem with X-hash encoder algorithm is which is applicable for only information contains words. Which cannot acceptable for bytes and bits inside the information. The below figure shows the X-Hash encoder algorithm which contains blocks in which data transferred in a word format.

Figure 1. X-hash encoder algorithm

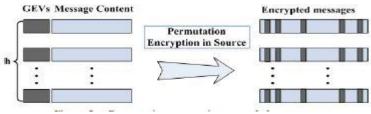

B. Deterministic linear network algorithm is used to create a security requirement at source side for weak signals. By this transmission rate increases but it cannot deals with intermediate nodes in a packet sent from the source code and also makes trouble for practical applications at the source code before data transmission. The below figure shows the deterministic linear network algorithm which contains frames in which contains data to be transferred with encryption format at source area.

Figure 2. Deterministic liner network algorithm.

C. The NMPC (Neural Markovian Predictive Compression) algorithm is used to compress the data in two phases they are Initial training and compression phase. Which is used at prefix of the input stream to be transferred, hence it is creating a security for the data.

```

NMPC(c[1, n]) {

i \leftarrow 1;

while (i \leq n) {

BNN \leftarrow c[i - I + 1, i - 1]; // \text{ in fact, normalized values}

if i > K\{// \text{ BNN and HMMs are already trained}

L \leftarrow BNN; // Building L by the BNN output layer

sort(L) in descending order of probabilities

\forall 1 \leq k \leq D

Forward(m_k, c[i - T + 1, i - 1]);

L \leftarrow HMMs; // Reassign the first D elements

sort( first D elements of L) // descending order of probabilities

y_i \longleftarrow \text{ index of } c_i \text{ in } L

code(y_i) // using adaptive coding

}

j \leftarrow \text{index of } c_i \text{ in } \Sigma \text{ (giving } c_i = \sigma_j \text{)}

v \leftarrow (-R, -R, \dots, R, \dots, -R) // j^{th} \text{ component is } R

Backpropagation (BNN, B, v);

Forward-Backward (m_j, c[i - T + 1, i - 1]);

if i \leq K // first K characters

output ci:

i++:

} // end of while

}

```

Figure 3.NMPC algorithm

D. Yuho Jin ,Ki Hwan Yum, Eun Jung Kim this paper proposed to compress the data with shared table algorithm. This takes more time to compress the data based on packet length. Which consumes more area which data stored in memory management system. The below figure shows the table shared algorithm method in which data compressed with two modules one with encoding another with decoding.

| value |       |        | inde                 | ex vec | tor    |                 |      |     |          |     |    |

|-------|-------|--------|----------------------|--------|--------|-----------------|------|-----|----------|-----|----|

| A     | 00    |        | 00                   | 01     | 01     |                 | 1    | 00  | <u> </u> | 00  |    |

| в     | 11 10 | 00     | 01                   | 00     | 11     | 11              | 10   |     | 01       | 10  | 11 |

| C     | 11    |        | 10                   | 3      |        | 01              | 01   |     |          | 1.3 | 10 |

| D     | 10    | 01     | 00                   |        | 10/    | 1               | 00   | 11  |          | 5 8 | l  |

|       | valu  | e inde | T                    | use-t  | oit ve | ctor<br>0 0 0 0 | 10   | 0   |          |     |    |

|       |       |        | Incodir              |        |        |                 | E4   |     |          |     |    |

|       | E     | 00     | 1100                 | 0 1 1  | 010    | 000             | 1 0  | 0   |          |     |    |

|       | A     | 01     | 0010                 | 1 0 0  | 0,0,0  | 0 1 0           | 0,0, | 1   |          |     |    |

|       | D     | 10     | 1000                 | 100    | 001    | 100             | 10   | 0   |          |     |    |

|       | B     | 11     | 0 1 0 0              | 1 0 0  | 0 1 0  | 000             | 1,0  | 1   |          |     |    |

|       |       |        |                      | -      | for F  | PE4             |      |     |          |     |    |

|       | Each  |        | cates a v<br>Decodin |        |        |                 |      |     |          |     |    |

|       | Fi    | igure  | 4. Tab               | le sh  | arec   | l alg           | ori  | thn | n.       |     |    |

# **III. DESCRIPTION OF DC COMPRESSION AND DC-DE-COMPRESSION ALGORITHM:**

By the above algorithms there is no guarantee for the data to compress at maximum level, and also which leads to consumes more area, it leads to introduce more delay and consumes more power. Hence this paper proposed an a algorithm as data compression (DC compression) and data compression de-compression (DC-Decompression).DC compression is a compression technique which compress the data at the transmission side by bit wise. DC-decompression is a technique which compresses the data at the receiver side based on the address location based.

#### **IV. CONCLUSION**

In the era of VLSI large number of cores has to implement on the single silicon die. Which is enhanced the need of on-chip caches [9-12]. Such large number of data has been implemented as a multitude of smaller blocks connected through a packet based (NoC) network–on-chip Developing memory management algorithms [13-15] will play important role in microprocessors. During data transfer we have to kinds of data will exists, like repeated entries, non-repeated data. This paper concludes that repeated data play a critical parameter to increase the performance of the system. Repetition of entries needs to avoid, Parallel data compression system requires more area on silicon chip, hence to manage speed, to enhance the large bandwidth, serial data compression system well suited for data management system.

#### **V.REFERENCES**

[1] Yuki Katsu and Haruhiko Kaneko "Low-Latency Lossless Compression for Data Buses Using Multiple-Type Dictionaries" in proceedings of 2016 Data Compression Conference DOI 10.1109/DCC.2016.68

[2] Ming He, Lin Chen, Hong Wang, Zhenghu Gong, Zhihong Liu "Survey on Secure Transmission of Network Coding in Wireless Networks" in proceedings of 2012 International Conference on Computer Science and Service System DOI 10.1109/CSSS.2012.308.

[3] Erez Shermer Mireille Avigal1 Dana Shapira "Neural Markovian Predictive Compression: An Algorithm for Online Lossless Data Compression," in *Proceedings of* 1068-0314/10 .2010 IEEE DOI 10.1109/DCC.2010.26, 2010.

[4] R. Das, A. K. Mishra, C. Nicopolous, D. Park, V. Narayan, R. Iyer, M. S. Yousif, and C. R. Das, "Performance and Power Optimization through Data Compression in Network-on-Chip Architectures," in Proceedings of HPCA, 2008.

[5] "International Technology Roadmap for Semiconductors," 2005.

[6] W. J. Dally and B. Towles, "Route Packets, Not Wires: On-Chip Interconnection Networks," in *Proceedings of DAC*, pp. 684–689, 2001.

[7] Y. Hoskote, S. Vangal, A. Singh, N. Borkar, and S. Borkar, "A 5-GHz Mesh Interconnect for a Teraflops Processor," IEEE Micro, vol. 27, no. 5, pp. 51–61,2007.

[8] D. Wentzlaff, P. Griffin, H. Hoffmann, L. Bao, B. Edwards, C. Ramey, M. Mattina, C.-C. Miao, J. F. B. III, and A. Agarwal, "On-Chip Interconnection Architecture

of the Tile Processor," IEEE Micro, vol. 27, no. 5, pp. 15–31, 2007.

[9] K. Sankaralingam, R. Nagarajan, H. Liu, C. Kim, J. Huh, D. Burger, S.W. Keckler, and C. R. Moore, "Exploiting ILP, TLP, and DLP with the Polymorphous TRIPS Architecture," in Proceedings of ISCA, pp. 422–433, 2003.

[10] M. B. Taylor, W. Lee, S. P. Amarasinghe, and A. Agarwal, "Scalar Operand Networks: On-Chip Interconnect for ILP in Partitioned Architecture." in *Proceedings of HPCA*, pp. 341–353, 2003.

[11] A. Kumar, L.-S. Peh, P. Kundu, and N. K. Jha, "Express Virtual Channels: towards the ideal interconnection fabric," in *Proceedings of ISCA*, pp. 150–161, 2007.

[12] P. Abad, V. Puente, J.-'A. Gregorio, and P. Prieto, "Rotary router: an efficient architecture for CMP interconnection networks," in *Proceedings of ISCA*, pp. 116–125, 2007.

[13] J. Kim, J. Balfour, and W. J. Dally, "Flattened Butterfly Topology for On-Chip Networks," in *Proceedings of MICRO*, pp. 172–182, 2007.

[14] D. N. Jayasimha, B. Zafar, and Y. Hoskote, "Interconnection Networks: Why They are Different and How to Compare Them," tech. rep., Microprocessor Technology Lab, Corporate Technology Group, Intel Corp, 2007.

[15] A. R. Alameldeen and D. A. Wood, "Adaptive Cache Compression for High- Performance Processors." in *Proceedings of ISCA*, pp. 212–223, 2004.